National Renewable Energy Laboratory

**Innovation for Our Energy Future**

# Processing Materials Devices and Diagnostics for Thin Film Photovoltaics: Fundamental and Manufacturability Issues

Final Report 1 March 2005 – 30 November 2008

R.W. Birkmire, W.N. Shafarman, E. Eser, S.S. Hegedus, B.E. McCandless, K.D. Dobson, and S. Bowden *University of Delaware Newark, Delaware*  Subcontract Report NREL/SR-520-45545 April 2009

# Processing Materials Devices and Diagnostics for Thin Film Photovoltaics: Fundamental and Manufacturability Issues

Final Report 1 March 2005 – 30 November 2008

R.W. Birkmire, W.N. Shafarman, E. Eser, S.S. Hegedus, B.E. McCandless, K.D. Dobson, and S. Bowden *University of Delaware Newark, Delaware*

NREL Technical Monitor: Bolko von Roedern Prepared under Subcontract No. ADJ-1-30630-12 Subcontract Report NREL/SR-520-45545 April 2009

National Renewable Energy Laboratory 1617 Cole Boulevard, Golden, Colorado 80401-3393 303-275-3000 • www.nrel.gov

NREL is a national laboratory of the U.S. Department of Energy Office of Energy Efficiency and Renewable Energy Operated by the Alliance for Sustainable Energy, LLC

Contract No. DE-AC36-08-GO28308

This publication was reproduced from the best available copy submitted by the subcontractor and received no editorial review at NREL

#### NOTICE

This report was prepared as an account of work sponsored by an agency of the United States government. Neither the United States government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States government or any agency thereof.

Available electronically at http://www.osti.gov/bridge

Available for a processing fee to U.S. Department of Energy and its contractors, in paper, from: U.S. Department of Energy Office of Scientific and Technical Information P.O. Box 62 Oak Ridge, TN 37831-0062 phone: 865.576.8401 fax: 865.576.5728 email: mailto:reports@adonis.osti.gov

Available for sale to the public, in paper, from: U.S. Department of Commerce National Technical Information Service 5285 Port Royal Road Springfield, VA 22161 phone: 800.553.6847 fax: 703.605.6900 email: <u>orders@ntis.fedworld.gov</u> online ordering: <u>http://www.ntis.gov/ordering.htm</u>

Printed on paper containing at least 50% wastepaper, including 20% postconsumer waste

## **List of Contributors**

#### **Principal Investigators**

Roger Aparicio Robert Birkmire Stuart Bowden Ujjwal Das Kevin Dobson Erten Eser Steven Hegedus Brian McCandless William Shafarman

## Researchers

Wayne Buchanan Shannon Fields Gregory Hanket Andrew McDermott

#### Visiting Scholars/Scientists

Vivian Alberts, Rand Afrikaans Univ., S. Africa Matt Edwards, Univ. of New South Wales Donghwan Kim, Korea Takashi Minemoto, Japan Cheikh Sene, Senegal Na Wei, Univ. of Stuttgart, China Datao Xie, China

#### **Post-Doctoral Fellows/Limited Term Researcher**

Stuart Bowden Estela Calixto-Rodriguez Ujjwal Das Mario Gossla Gautam Ganguly Jonathan Frey Moses Haimbodi Gregory Hanket Sukti Hazra Yunhe Huang Kyoung Kim Sylvain Marsillac Takashi Minemoto Shiro Nishiwaki Puthar Devassey Paulson Sergey Rykov Baosheng Sang Nick Smith Alex Stavrides Udai Singh

## **Technical Support**

Joshua Cadoret Charles Debo Vicky Dinetta Ronald Dozier Shannon Fields Kevin Hart Thomas Hughes-Lampros Dan Ryan

## **Graduate Students**

Michael Burrows Darshini Desai Jeff Doody Ozgenc Ebil Dan Esposito Xin Fan Jonathan Frey Moses Haimbodi Rong Xue Huang Mike Humbert Toby Junker Rui Kamada Pengcheng Lv Meijun Lu Kapil Mukati Sarah Rickman Brent Shu Scott Stephens Jochen Titus Christopher Thompson James Wilson Eva Wu Dong Xu Clifford Yapp Mike Zellner

#### **Undergraduate Students**

John Allen Michael Angelo Sirinivasan Balakrishnan Tyreef Bevel Derek Birkmire Joshua Cadoret William Crandley Brad Culver Andrew Damiani John Dellose Stephanie Einstein Grant Fisher Jonathan Frey Jennifer Griffith Yannick Goue Sonam Gupta Juanita Jablasone Brian Kennedy Mary Kondos **Timothy Miller** Kunal Modi Adam Murauskas Adam Palanker Laura Robinson Dan Ryan Dan Sadowsky Chelsea Saunders David Silowka Kevin Tran Brian Wagner Haoshu Wang James Wilson Chati Zony

## **Document Preparation**

Linda Granger Steven Hegedus L. Bonnie Johnston Elaine Koronik Teresa Sharp Tritt

| List | of Contributors                            | <u>Page</u><br>iii |

|------|--------------------------------------------|--------------------|

| Tabl | le of Contents                             | vi                 |

| Abs  | tract                                      | viii               |

|      |                                            |                    |

| 1    | Objectives, Training, and Publications     | 1                  |

|      | 1.1 CdTe/CdSe-based Solar Cells            | 1                  |

|      | 1.2 CuInSe <sub>2</sub> -based Solar Cells | 1                  |

|      | 1.3 Si-based Solar Cells                   | 1                  |

|      | 1.4 In-line Diagnostics                    | 3                  |

|      | 1.5 Training and Education                 | 4                  |

|      | 1.6 Publications                           | 4                  |

|      | 1.7 Thin Film Partnership                  | 4                  |

|      | 1.8 Organization of the Report             | 4                  |

| 2    | CdTe Based Solar Cells                     | 5                  |

|      | 2.1 Phase 1 Summary: 9/5/01 to 9/4/02      | 5                  |

|      | 2.2 Phase 2 Summary: 9/5/02 to 9/4/03      | 10                 |

|      | 2.3 Phase 3 Summary: 9/5/03 to 9/4/04      | 13                 |

|      | 2.4 Phase 4 Summary: 9/5/04 to 9/4/05      | 17                 |

|      | 2.5 Phase 5 Summary: 9/5/05 to 3/31/07     | 20                 |

|      | 2.6 Phase 6 Summary: 4/1/07 to 12/31/07    |                    |

|      | 2.7 Phase 7 Summary: 1/1/08 to 5/31/08     | 23                 |

|      | 2.8 References                             |                    |

| 3    | CIS-based Solar Cells                      |                    |

|      | 3.1 Phase 1 Summary: 9/5/01 to 9/4/02      |                    |

|      | 3.2 Phase 2 Summary: 9/5/02 to 9/4/03      | 41                 |

|      | 3.3 Phase 3 Summary: 9/5/03 to 9/4/04      | 43                 |

|      | 3.4 Phase 4 Summary: 9/5/04 to 9/4/05      | 45                 |

# **Table of Contents**

|   | 3.5 Phase 5 Summary:   | 9/5/05 to 3/31/07  | 49 |

|---|------------------------|--------------------|----|

|   | 3.6 Phase 6 Summary:   | 4/1/07 to 12/31/07 | 52 |

|   | 3.7 Phase 7 Summary:   | 1/1/08 to 5/31/08  | 54 |

|   | 3.8 References         |                    | 61 |

| 4 | Si-Based Solar Cells   |                    | 62 |

|   |                        | 9/5/01 to 9/4/02   |    |

|   | 4.2 Phase 2 Summary:   | 9/5/02 to 9/4/03   | 64 |

|   | 4.3 Phase 3 Summary:   | 9/5/03 to 9/4/04   | 66 |

|   | 4.4 Phase 4 Summary:   | 9/5/04 to 9/4/05   | 69 |

|   | 4.5 Phase 5 Summary:   | 9/5/05 to 3/31/07  | 69 |

|   | 4.6 Phase 6 Summary:   | 4/1/07 to 12/31/07 | 71 |

|   | 4.7 Phase 7 Summary:   | 1/1/08 to 5/31/08  | 72 |

| 5 | In-Line Diagnostics an | d Process Control  | 80 |

|   | 5.1 Phase 1 Summary:   | 9/5/01 to 9/4/02   | 80 |

|   | 5.2 Phase 2 Summary:   | 9/5/02 to 9/4/03   | 80 |

|   | 5.3 Phase 3 Summary:   | 9/5/03 to 9/4/04   | 81 |

|   | 5.4 Phase 4 Summary:   | 9/5/04 to 9/4/05   | 82 |

|   | 5.5 Phase 5 Summary:   | 9/5/05 to 3/31/07  | 82 |

|   | 5.6 Phase 6 Summary:   | 4/1/07 to 12/31/07 | 83 |

|   |                        |                    |    |

| 6 | Publications | 8 | 85 |

|---|--------------|---|----|

|---|--------------|---|----|

#### Abstract

This report describes results achieved under this subcontract to develop and understand thin film solar cell technology associated to CuInSe<sub>2</sub> and related alloys, a-Si and its alloys and CdTe. This includes application of a-Si to c-Si wafer-type cells as well. Modules based on all these thin films are promising candidates to meet DOE long-range efficiency, reliability and manufacturing cost goals. The critical issues being addressed under this program are intended to provide the science and engineering basis for the development of viable commercial processes and to improve module performance. The generic research issues addressed are: 1) quantitative analysis of processing steps to provide information for efficient commercial scale equipment design and operation; 2) device characterization relating the device performance to materials properties and process conditions; 3) development of alloy materials with different bandgaps to allow improved device structures for stability and compatibility with module design; 4) development of improved window/heterojunction layers and contacts to improve device performance and reliability; and 5) evaluation of cell stability with respect to illumination, temperature and ambient and with respect to device structure and module encapsulation.

# **1 OBJECTIVES, TRAINING, AND PUBLICATIONS**

The primary objectives of the NREL-sponsored research at the Institute of Energy Conversion (IEC) research are listed below according to the specific 3 types of thin film solar cells currently under commercial interest. In addition, generic process diagnostic and control tools will be developed. Student training and publication statistics are also summarized.

# 1.1 CdTe/CdSe-based Solar Cells

The CdTe effort will address increased voltage and stability, the development of an inline CdTe process to implement high rate and high throughput deposition on a moving substrate, and fundamental studies of CdTe surface chemistry. To meet these objectives, IEC will:

- Separate and quantify the effect on  $V_{OC}$  of high resistance (HR) buffer layers such as  $Ga_2O_3$  and  $In_2O_3$  and widening the CdS window layer bandgap with Zn.

- Develop and apply a transparent back contact to CdTe to probe back contact junction formation and degradation.

- Evaluate methods for increasing  $V_{OC}$  by reducing space charge recombination.

- Conduct detailed analysis of collection losses using conventional and bifacial devices, AMPS modeling, and JV measurements under different conditions.

- Improve the stability of CdTe devices by developing alternative processing steps to 'stabilize' the junction and contact; and to compare the effects of well-controlled stress conditions on CdTe solar cells by performing detailed device analysis and relating results to differences in fabrication.

- Develop the fundamental understanding needed for high throughput CdTe module fabrication by controlling high rate delivery of Cd and Te species to the moving substrate surface.

- Develop rapid and reproducible post-deposition processing alternatives to the current CdCl<sub>2</sub> vapor treatment.

- Determine fundamental understanding of etching and wet processing steps on CdTe surfaces

- Determine relation between the contact processing and CdTe surface chemistry, and the device performance and stability especially as applies to First Solar devices.

# 1.2 CulnSe<sub>2</sub>-based Solar Cells

The CuInSe<sub>2</sub>-based effort will characterize fundamental properties of interfaces in CuInSe<sub>2</sub>-based solar cells, develop approaches to improving  $V_{OC}$  including alloying with S and Al, and will also include the development of an in-line process for deposition on a moving substrate. To meet these objectives, IEC will:

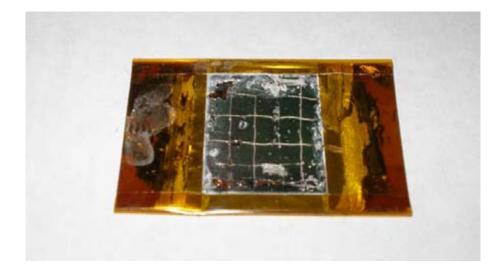

- Develop the in-line deposition of Cu(InGa)Se<sub>2</sub> films from stationary elemental evaporation sources onto moving rigid (Mo coated glass) and flexible (Mo coated polyimide) substrates at rates commensurate with commercial manufacturing.

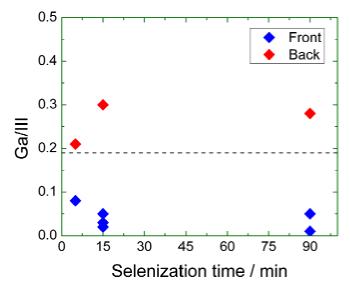

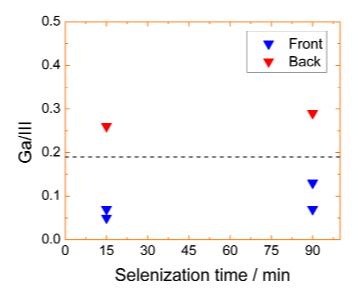

- Determine the relationship of the film properties, both compositional and structural, to the solar cell performance with particular emphasis on the effect of complex band-gap profiles due to the depth distribution of Ga and In and incorporation of Na.

- Increase the operating voltage by increasing the bandgap,  $E_g$ , in the absorber layer or in the space charge region using Cu(InAl)Se<sub>2</sub> alloys.

- Investigate the feasibility of controlled p-type doping of the Cu(InGa)Se<sub>2</sub> or Cu(InAl)Se<sub>2</sub> absorber layers to increase V<sub>OC</sub>.

- Provide a fundamental understanding of surface reactions and interface chemistry in the fabrication of CIGS devices using atomic level surface characterization techniques to study the Mo surface, Mo/ Cu(InGa)Se<sub>2</sub> interface, the free Cu(InGa)Se<sub>2</sub> surface and Cu(InGa)Se<sub>2</sub>/CdS interface.

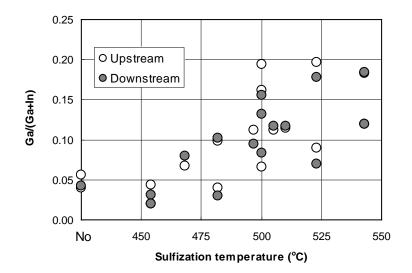

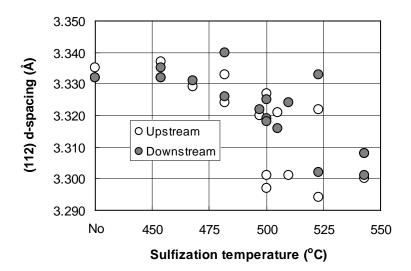

- Determine reaction pathways for the formation of Cu(InGa)Se<sub>2</sub> and Cu(InGa)(SeS)<sub>2</sub> on H<sub>2</sub>Se/H<sub>2</sub>S time-temperature-gas concentration profiles using sputtered Cu/Ga/In precursors.

- Fabricate devices with CdS, ZnS, and CdZnS buffer layers and CuInSe<sub>2</sub> with Ga, S, and/or Al alloy absorber layers in order to characterize the effect buffer layers on device behavior and fundamental interface properties.

# 1.3 Si-based Solar Cells

The Si-based effort will focus on developing a process for fabricating polycrystalline Si solar cells and materials at low temperatures on low cost substrates as well as the use of microcrystalline Si layers in solar cells. To meet these objectives, IEC will:

• Develop in-situ and/or post-deposition methods such as metal induced crystallization (MIC) to produce HWCVD deposited Si films and devices with grains in the micrometer range.

- Investigate various forms of Eutectic Promoted Deposition (EPD) where very thin metal layers deposited on glass substrates are briefly heated above the metal-Si eutectic as the HWCVD Si deposition proceeds leading to precipitation of Si from the supersaturated liquid solution.

- Investigate the feasibility of layer-by-layer deposition (LBL) to create thin Si seed layers in-situ to enhance nucleation of larger grains during subsequent growth.

- Develop all HWCVD p n junction devices by developing HWCVD emitter layers on large grain HWCVD absorbers.

- Develop processing of c-Si heterojunction solar cells using PECVD deposited emitters and contacts with increased V<sub>OC</sub>.

- Investigate alternative contact structures for c-Si solar cells utilizing improved passivation.

- Investigate chemical surface treatments leading to high effective lifetimes.

- Develop texturing approaches compatible with effective passivation.

## 1.4 In-line Diagnostics

The in-line process diagnostic effort will develop diagnostic tools needed for process control and the associated quantitative models that link sensor outputs to process variables and material properties. To meet these objectives, IEC will:

- Understand the fundamentals of thin film growth and identification of critical properties that lead to efficient solar cells, i.e., product specifications.

- Identifying process parameters, to which film properties are sensitive, i.e., process determinants.

- Develop robust, reliable and fast-response sensor equipment for in-situ applications in deposition reactors.

- Develop quantitative models that relate sensor output to process determinants and film properties for use in model based process control, i.e., intelligent process control.

# 1.5 Training and Education

During the period of this subcontract (September 5, 2001 to May 31, 2008) IEC provided training and education for the following: 7 visiting professionals, 2 of which were Fulbright scholars; 20 post-doctoral fellows/limited term researchers; 25 graduate students; and 33 undergraduate students. A complete list of names is given in the list of contributors.

# 1.6 Publications

As a result of research performed under this contract, IEC published 140 papers. See the complete list under Section 6.

# 1.7 Thin Film Partnership (TFP) Team Activities and Collaborations

Since IEC was a major contributor to the NREL Thin Film Partnership (TFP) Teams, our collaborations and activities in this area are discussed in each Phase for each of the three teams (CdTe, Cu(InGa)Se2, and Amorphous and Thin Si). IEC staff served as Leaders of various sub-teams within each of the above teams. Reviews of various topics of interest were prepared and presented at the team meetings. The considerable collaborations between IEC with other universities and industrial groups resulted in publications, demonstrated improvements in technology, and mutual benefit to National Thin Film Partnership. Several graduate students who received their training at IEC funded by the TFP are now working in the US PV industry.

# **1.8 Organization of the Report**

This report contains the summary of results from the first 6 Phases of this contract. They are each organized into four technical sections: CdTe-based solar cells, CuInSe<sub>2</sub>-based solar cells, Si-based solar cells, and In-line Process Diagnostics. More complete details can be found in the Annual Reports for each phase which are posted on the IEC website whose link is given. Following the summary of each previous Phase, detailed results from the final Phase, January 01, 2008 to May 31, 2008 is given.

# 2 CdTe-BASED SOLAR CELLS

#### 2.1 Phase 1 Summary: 9/5/01 to 9/4/02

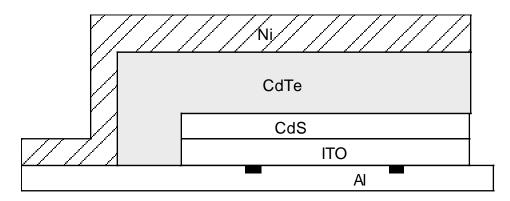

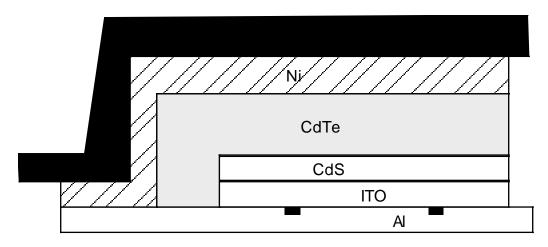

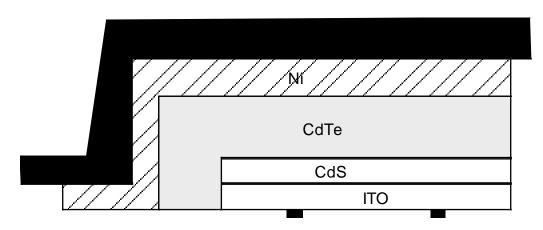

The influence of the high resistance (HR) layer and CdS layer was studied using detailed analysis of J(V) measurements. A series of devices were fabricated with 40 or 80 nm of Ga<sub>2</sub>O<sub>3</sub> or In<sub>2</sub>O<sub>3</sub> HR layers having 0 or 80 nm CdS. Cells without CdS had V<sub>oc</sub>~0.1-0.2 V and very large voltage dependent photocurrent suggesting a very low built in field. Reverse bias of -2V was needed to saturate the QE of cell without CdS. Analysis of temperature and intensity dependent J(V) and  $V_{oc}(T)$  showed that devices with CdS have much higher A factors compared to CdS-free devices (1.6-2.0 compared to 1.1-1.2) and 4 orders of magnitude lower  $J_0$ . The activation energy for recombination  $\phi$  /A was obtained from an Arrhenios plot of  $J_0$  where  $\phi$  should equal the bandgap for SRH recombination. Values of  $\phi/A$  for 0 and 80 nm CdS were 0.54 and 0.73 eV, respectively. The value of  $\phi/A=0.73$  eV is near mid gap consistent with the A factors close to 2. This indicates the CdS devices are limited by SRH type recombination but the CdS-free devices are limited by a different mechanism. The intercepts of  $V_{oc}$  vs T are  $\phi/q \sim 1.4$  V and  $\sim 0.6$  V for CdS and CdS-free devices. This confirms that the CdS device has SRH recombination since the intercept  $\phi = \text{Eg of CdTe}$ . The CdS-free device has a much lower barrier which explains the poor voltage dependent collection hence low FF and a different recombination mechanism  $(A \sim 1)$  than CdS devices  $(A \sim 2)$ . One possibility is interface recombination. No clear difference between In<sub>2</sub>O<sub>3</sub> or Ga<sub>2</sub>O<sub>3</sub> was found.

The effects of adding extra Cu into the cell structure to simulate the high Cu throughout the cell structure, as may occur during device stressing, was studied. Devices were processed with thin Cu films deposited between either the ITO and CdS layers or between the CdS and CdTe layers, and contacts were deposited following IEC's baseline recipe. Initial results showed devices with extra Cu films all exhibited low V<sub>oc</sub>, attributed to high doping of the cell junction region, and strong J-V rollover compared to control cells. Cu was observed to diffuse to the back (CdTe) surface of the cell during processing, so the presence of Cu oxides at the back surface may account for the observed rollover. Structural investigations also determined changes in CdS crystal structure when deposited on Cu films compared to CdS deposited on ITO. Later studies to isolate the cause of rollover in the cells were hindered by shunting and poor adherence of the CdTe/CdS layers. QE measurements on the initial set of cells showed that the presence of the thin Cu films in the cell structure had a profound effect on the photocarrier recombination and transport with some similarities to Cu-sensitized photoconductive CdS and suggests that much smaller amounts of Cu present in the cell structure could lead to degradation in device behavior.

The possibility of photoconductive CdS was studied further using the bias light spectrum of QE. An enhancement of the blue response by red bias light was found in devices from BP Solar, First Solar, and Institute of Energy Conversion. The effect becomes more pronounced after stress, and at MP more than SC. The QE can easily exceed unity

indicating this is a secondary photoconductive effect. No such effect was seen for CdSfree devices. This gives motivation for further study of Cu-doped CdS since it may give insight into stress-related degradation.

With stress, Cu<sub>2</sub>Te back contacts on CdTe/CdS solar cells have been previously observed to transform to the less favorable CuTe species (an oxidation process). A new approach to stabilizing back contacts was begun using additives in the back contact paste to preserve the Cu<sub>2</sub>Te back contact by surface complexation or redox chemistry. Cells were prepared containing a range of additives, including a number of complexing and reducing agents, in the carbon paste contact. Initial device processing determined that complexing agents scavenged Cu from the back contacts, which resulted in poor performance (either initially following contact processing or following short thermal stress) including significant J-V rollover. Cells contacted with pastes containing reducing agents showed, with stress, an attenuation of the formation of J-V rollover compared to control cells. These results highlight that CdTe/CdS device performance can be significantly affected by the presence of a small amount of chemically active species in the back contact. Attempts to stabilize back contacts by using Cu compounds and complexes as additives in the paste as both the source of Cu and the stabilizing species were not successful. However, these results highlighted that Cu powder and Cu(I) salts (e.g. CuCl, CuI) could form a favorable back contact, whereas, due to their higher stability, Cu(II)-complexes could not.

An investigation of the action of NP and  $Br_2$ -meth etching on CdTe has been carried out. Variable Angle Spectroscopic Ellipsometry (VASE) and Glancing Incidence X-ray Diffraction (GIXRD) were applied to investigate effects of etching on CdTe surfaces. It was found that etching in 1% NP (NP1) for >40s resulted in the formation of relatively thick crystalline Te surface layers. With shorter times, the initial Te surface layer contained a higher degree of amorphous phase which spontaneously crystallizes over time following removal from the etch solution. In contact with ambient atmospheric conditions, the NP etched surface was stable to oxidation for ~3-4 h. By comparison, Br<sub>2</sub>-meth etching produces a very thin Te-rich layer on CdTe, which begins to oxidize immediately following removal from solution. As NP etching proceeds, bubbling (NO(g) or NO<sub>2</sub>(g)) begins on the CdTe surface. The commencement of bubbling coincides with significant formation and consumption of Te.

GB etching can be a problem associated with cells that have received NP etching. We have attempted to adjust the NP etch properties to reduce effects of GB etching. The initial approach was to increase the acidity of the etch solution, to allow fast formation of the Te surface layer over very short immersion times. Higher acidity etches could produce surface levels of Te similar to NP1 following just 2-6s immersion. SEM confirmed no GB widening had occurred at these times, but did occur at immersion times >8s. Test-tube reactions also suggest that the higher acidity etches may proceed via a different mechanism.

A further approach to slowing GB etching is the use of high viscosity etch solutions. An investigation of the effect of using solutions of varying viscosity on the action of  $Br_2$  on

CdTe surfaces has begun. Increasing solvent viscosity will slow the rate of GB diffusion of the etchant. AFM and VASE measurements indeed show that the rate of CdTe etching is slowed in etch solutions prepared with higher viscosity solvents.

There is a clear need to establish better correlation between accelerated stressing performed in the lab and conditions experienced in the field. Typically, lab stressing has been done at 70-100°C in a continuous manner while modules in the field see temperatures from 20-60°C with cyclic (daily) light exposure and power generation. It is possible that some relaxation effects might occur during the dark portion of the cycle which would result in lower or negligible degradation for cyclically stressed devices. Therefore, we designed a series of stress experiments with various cycles of light (L), dark (D) and temperature (65° or 20°C). Two sets of BP and FS devices (i.e. with their own contact) were stressed at each of the above conditions for 30 days. In each stress, there was one at OC and at 1/2 OC bias. V<sub>oc</sub> was monitored at 65°C after the 8 or 16 hours of dark and 16 or 8 hours of light to see if there was any relaxation or recovery after short periods of darkness. A key result, identified for the first time, is that  $V_{oc}$  after daily OC stressing in both FS and BP devices can show a daily variation, repeated every day for 30 days. We observed a 30-50 mV recovery in Voc during 16 hours of darkness, followed by 30-50 mV decrease in  $V_{oc}$  during 8 hours illumination. Degradation with stress for FS or BP cells is not simply correlated to the exposure time. For FS devices, the stability is strongly bias dependent. Bias at 1/2 OC is nearly stable while OC is very unstable. One type of FS devices shows recovery of  $\sim 50$  mV in V<sub>oc</sub> with nightly periods of dark while the other does not. We also analyzed the dark JV curves of the FS devices. Before stress, we found typically A=1.5,  $R_s$ =4-5  $\Omega$ -cm<sup>2</sup>, and  $J_0$ =1E-10 A/cm<sup>2</sup>. After stress, we found differences depending on the bias during stress, but not so clearly on the stress cycle. FS cells stressed at OC showed: an increase in A factor from 1.5 to 1.9, no change in  $R_s$ , and either a decrease or increase in  $J_0$  of 10-100X. We have never before seen a decrease in J<sub>o</sub> with stress on FS devices, but this is consistent with the increase in V<sub>oc</sub> of 30-60 mV. No blocking contact was observed in the dV/dJ plots. In contrast to FS, stability in BP devices has a very weak bias dependence, instead correlating with time at 65°C more than bias. They also show partial recovery in  $V_{oc}$ ~30 mV overnight and nearly complete recovery after a week in the dark at room temperature. Degradation is nearly all in  $V_{oc}$ . Analysis of J(V) curves for BP devices showed a consistent increase in A factors from 1.9 to 2.2 and in  $J_0$  from 1E-9 to 2E-8 A/cm<sub>2</sub> with stress. There was no significant increase in  $R_s$  and no blocking contact curvature observed after stress.

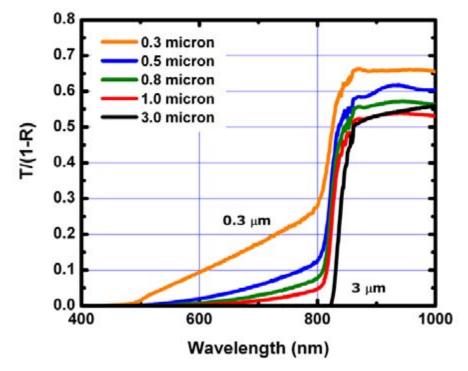

The properties of vapor transported CdTe films deposited onto moving CdS/ITO/glass superstrates were determined for different deposition temperatures and growth ambients. A vapor transport deposition (VTD) system was used to deposit onto a 10 cm wide translating substrate at temperatures from 450°C to 550°C. For depositions in pure He, the roughness increased with substrate temperature and film texture changed from (111) at low temperature to (220) at high temperature. Deposition in He+O<sub>2</sub> ambient produced smoother films, even at greater film thickness, with near-random texture. Unlike PVD films, which exhibit in-plane compressive strain, the lattice parameter in VTD films is equal to that for pure unstrained CdTe. The VTD films exhibit a sharp optical absorption edge with 60-70% sub-band gap absorption.

A first-order model for VTD radiative transfer within the source and for VTD CdTe film deposition with a carrier gas was developed. CdTe films were deposited at ~1  $\mu$ m/min static equivalent deposition rate onto CdS/ITO/glass superstrates translating 1 cm/min beneath the source. The radiative model was used to optimize the filament geometry within the source. The mass transfer model and measured source effusion verify that the source operates by saturation of the carrier gas with Cd and Te<sub>2</sub> vapor. CdTe/CdS devices were fabricated using VTD CdTe films deposited at different substrate temperatures and ambient to establish baseline conditions. This has yielded cells with ~11% efficiency for deposition at 550°C in He+O<sub>2</sub> ambient. Deposition at higher substrate temperature onto window layers incorporating high resistance buffer layers is expected to yield high conversion efficiency devices to serve as a baseline for further optimization.

## CdTe TFP Team Activity and Collaboration

IEC attended the 14<sup>th</sup> CdTe TFP Team Meeting, held at the Florida Solar Energy Center in Cocoa, Florida. We made presentations on results of activity in three sub-teams, and on cyclic stressing of CdTe devices, as detailed below. Detailed results are presented in the CdTe Team Minutes.

#### Stressing Sub-team

Considerable work involving cyclic stressing was performed on BP and FS samples. Some was reported in the Annual Report, at the 14<sup>th</sup> CdTe TFP Team Meeting, and privately to the two companies.

#### Micrononuniformity sub-team

First Solar provided various groups with pieces in unstressed and stressed condition. We analyzed cells from pieces FS-B11080213-K4B (unstressed) and -K5A (stressed). We found that with stress, the diode recombination  $J_o$  increases by 3-4 orders of magnitude from ~1x10<sup>-10</sup> to  $1x10^{-6}$  mA/cm<sup>2</sup> and A increases from 1.6 to 2.0. The series resistance increased from 3 to 6  $\Omega$ -cm<sup>2</sup> and blocking contact behavior appeared. The intercept of  $V_{oc}$  vs. T decreased from 1.53 to 1.48 eV. These results are very consistent with other results we have obtained from FS devices over the years either with their contact (like these) or with IEC contact, which had been stressed either at FS or at IEC.

We also analyzed sputtered CdTe devices from University of Toledo having Cu/Au contacts. Piece 971B was in the initial state and 966C was stressed. Stressing was performed at UT for 27 days at 60°C at 1 sun at OC. UT provided us with their JV data. We found that the stressed devices had recovered in  $V_{oc}$  and FF in the month between testing at UT and at IEC. Efficiency was ~11.6% initial and ~11.2% stressed. This represents surprisingly good stability for Cu/Au contacts. Devices had curvature in dV/dJ even in initial state. Series resistance increased from 2 to 4  $\Omega$ -cm<sup>2</sup> and J<sub>0</sub> increased from  $1 \times 10^{-7}$  to  $3 \times 10^{-6}$  mA/cm<sup>2</sup> with stress. CV under different bias light conditions indicated

the CdTe is completely depleted even at 0V in the light, suggesting a carrier density less than  $1 \times 10^{14}$  cm<sup>-3</sup>. This is similar to BP devices. In contrast, FS devices require -3 V for depletion and have carrier densities of  $-5 \times 10^{14}$  cm<sup>-3</sup>. Carrier density decreases with stress in FS devices.

We summarize our findings for FS, BP and UT devices regarding grain size, stability, dark recovery, carrier density, and deposition methods. We note the following correlation: BP and UT devices have small grains and similar stability and carrier density despite having very different deposition and contact processing. FS devices, measured so far, have larger grains, poorer stability, very strong bias dependence to stressing, and higher carrier density.

#### CdCl<sub>2</sub> Sub-Team

A post deposition treatment matrix was employed to systematically determine the role of CdCl<sub>2</sub> and air processing on electrodeposited films supplied by BP Solar and PVD films supplied by Canrom. For the BP Solar CdTe/CdS, cells were fabricated using CdTe/CdS from a single Apollo plate (3144) by varying treatment ambient, temperature, and time. AFM and GIXRD were used to characterize the film morphology and phase content prior to contacting. Back contacts were fabricated using the Cu-diffusion process, with Acheson 505SS C ink conductor. For cells with no treatment at all, low photocurrent was obtained. For single-step air heat treatments,  $J_{sc} < 15 \text{ mA/cm}^2$  were obtained with  $V_{oc} < 700 \text{ mV}$ . For single-step CdCl<sub>2</sub>:Air vapor treatments, higher photocurrents,  $J_{sc} \sim 20 \text{ mA/cm}^2$  and  $V_{oc} > 700 \text{ mV}$ . These results are qualitatively similar to those found for PVD films. The best cells had efficiency >11%.

For the Canrom CdTe/CdS, a small set of samples was surveyed using single-step CdCl<sub>2</sub>:Air treatment and two-step treatment, with either a 600°C anneal in argon, or 450°C air treatment prior to the CdCl<sub>2</sub>:Air treatment. For this material, the best cells had 7% efficiency, obtained with the single-step treatment in CdCl<sub>2</sub>:Air. Surprisingly, the two-step processes yielded efficiencies less than 6%, suggesting that the higher temperatures may electrically activate an unknown contaminant in the structures.

#### Capacitance Sub-Team

Measurements of C(V) under various bias light conditions were performed on FS, BP and UT devices in initial and stressed states. Significant differences were observed in C-V behavior. Results were presented at the March 2002 Team Meeting and published in the minutes.

## 2.2 Phase 2 Summary: 9/5/02 to 9/4/03

Investigations of the dynamics of CdTe etching have continued. Variable Angle Spectroscopic Ellipsometry (VASE) has shown that bromine-methanol (BM) etching to be consistent and very reproducible. BM polishing of CdTe will be used for sample preparation for a systematic investigation of nitric-phosphoric (NP) etching of CdTe, to accurately determine Te thickness.

A number of devices, contacted with Cu-containing graphite paste, were prepared to monitor the effects of different etch treatments on cell performance and stability. Devices processed from Br<sub>2</sub>-based etches of high viscosity, and hence extremely thin Terich surface films, were found to shunt within a few hours of processing, due to the inability of the thin Te to getter Cu. Devices processed using NP etches of different times, and contacted with Cu-containing graphite paste, initially all showed similar performance. Following stressing, no decrease of  $V_{OC}$  or  $J_{SC}$  was observed, however, the  $R_{OC}$  of devices that had received shorter NP etches had significantly increased, while longer etched samples showed very little change in  $R_{OC}$ . These changes are indicative of back contact degradation and again suggest that devices with back contacts processed with thicker Te components will exhibit improved stability due to improved Cu gettering and compensation of other chemical changes.

The chemistry of Cu with Te-rich CdTe surfaces, prepared by different etch treatments, was investigated. The Cu was supplied from graphite paste contacts. Differences in the copper telluride product were observed, dependent on etch type and chemical nature of Cu. The thicker Te-rich layer formed by NP etching results in a higher degree of the CuTe phase, on reaction with Cu-powder or Cu salts in the graphite paste, compared to BM etching. CuCl and CuI appear to form  $Cu_{2-x}$ Te on BM etched CdTe, while Cu powder forms CuTe. Initial results were complicated by the presence of residual crystalline graphite from the paste, however this residue can be easily removed.

Effects of stressing cell components and completed devices in conditions of varying humidity were monitored. TeO<sub>2</sub> and CdTeO<sub>3</sub> were found to be formed at lower humidities on CdTe, while the formation of amorphous hydroxide, oxide or hydrate phases are more likely at higher humidities. The IEC back contact appears to be stable at higher humidities, but is oxidized to TeO<sub>2</sub> at low humidity. This suggests that copper tellurides are more susceptible to oxidation by atmospheric oxygen. However, despite the extensive chemical changes observed, device performance was almost unaffected. In contrast, First Solar devices showed significant degradation. The robustness of the IEC back contacts is proposed to be due to the thick, 100 nm, Te film present in the back contact, which compensates chemical changes to the contact.

High efficiency CdTe/CdS devices require a robust and durable thin CdS film, which maintains a continuous layer for uniform junction formation. We investigated the relationship between device processing, materials properties and device performance for cells with CdS films deposited by chemical surface deposition (CSD), which produces conformal ultra-thin CdS films with low particulate density and high utilization of Cd

species. In CSD, a solution at ambient temperature is applied to a pre-heated glass/TCO substrate. Film deposition proceeds by heterogeneous nucleation at the surface as heat is transferred to the solution. Heat loss from the solution to the ambient helps maintain conditions favorable for film growth over the time needed typically ~ 5 min. The focus has been on establishing and understanding baseline processing procedures for the CdS/TCO superstrates and post-deposition procedures for completed CdTe/CdS structures. The processing variables investigated here for CdS/TCO were time and temperature of the CdCl<sub>2</sub> treatment given to the CSD CdS prior to CdTe deposition and use of a high temperature anneal (HTA) step. Measurements of a film 90 nm thick CdS films on Ga<sub>2</sub>O<sub>3</sub>/SnO<sub>2</sub>/glass before and after vapor CdCl<sub>2</sub> treatment at 430°C shows significant recrystallization based on sharpening of the transmission band-edge and sharpening of diffraction peaks (GIXRD). It was found that CdS films grown on Ga<sub>2</sub>O<sub>3</sub> have larger grain size than those on glass.

Having established that  $CdCl_2$  treatments change the CdS properties, we optimized the device performance by varying  $CdCl_2$  temperatures (350-430°C) and times (5-20 minutes). In general, efficiency improved with increasing the temperature and time. Therefore, a temperature of 430°C and time of 20 min was selected for CdS treatment in subsequent studies.

Since the CdS is deposited from a Cl based-solution, it was possible that a HTA would be sufficient to activate the CdS grain growth against further interdiffusion, thus, eliminating the need for a separate CdCl<sub>2</sub> treatment of the CdS. Devices were made with and without the HTA and CdCl<sub>2</sub> treatments to CdS prior to CdTe deposition. The CdS CdCl<sub>2</sub> treatment was at 430°C for 20 min and the HTA was at 550° for 30 min in Ar. Also included in this study were substrates of glass/SnO<sub>2</sub>/CdS from First Solar. They did not receive any treatments since the CdS was deposited at high temperature. J-V results showed that cells with the CdS HTA alone or in combination with CdCl<sub>2</sub> had reduced FF. The best cell on three identically processed pieces with CdCl<sub>2</sub> only (no CdS HTA) ranged from 10-11%. Yields were better than 75%. Cells with HTA had 9-10% efficiency. Devices on First Solar CdS had similar  $V_{OC}$  and FF to cells on CSD CdS. We conclude that our CSD CdS is not a major limitation to higher  $V_{OC}$  or yield at this time providing it has a CdCl<sub>2</sub> pre-treatment.

We are continuing to investigate the relationship between CdTe deposition and film properties for cells with CdTe deposited at a high rate on moving substrates by vapor transport (VT). The VT deposition process is similar but not identical to that used at First Solar. The influence of He and O<sub>2</sub> flow rate (2% O<sub>2</sub>/He) and pressure during the CdTe growth was investigated using AFM, GIXRD and contact wetting angle. As compared to the baseline run, increasing the total flow of helium through the source, results in a substantial decrease in grain size. Decreasing the total flow of He yields slightly larger, more densely packed CdTe grains. Increasing the ratio of helium to oxygen by two, results in larger less densely packed grains. Device results from these runs are pending.

The relation between device processing and device performance for cells with VT CdTe deposited at a high rate on moving substrates has focused on establishing and

understanding baseline processing for the post-deposition procedures of completed CdTe/CdS structures. For the CdTe/CdS post-deposition treatments, the time and temperature of the CdCl<sub>2</sub> treatment, use of a HTA prior to CdCl<sub>2</sub> treatment, and spacing between the CdCl<sub>2</sub> plate and CdTe surface were investigated. Following deposition of a ~4  $\mu$ m CdTe layer at 550°C in a single 6 minute pass in He/O<sub>2</sub> at 20 T, pieces receive a HTA and/or CdCl<sub>2</sub> treatment. Contact processing consists of a BDH etch then loading the samples into the evaporator for the layered back contact structure of 50 nm Te, 30 nm Cu, 50 nm Au. Post-contacting annealing was investigated, and a 30 minute anneal in Ar at 190°C was found to be optimum.

The time and ambient of the CdCl<sub>2</sub> treatment at 430°C of the completed CdS/CdTe structure was varied from 0 to 60 minutes in either dry or moist air. It was found that the HTA by itself (no CdCl<sub>2</sub> treatment) accomplished the same enhancement in performance, to ~8% efficiency, as the optimum CdCl<sub>2</sub> treatment in this experiment. A device with neither HTA nor CdCl<sub>2</sub> had poor FF and poor collection from the CdTe. There was no clear difference in device performance between dry or moist air during the CdCl<sub>2</sub> treatment, suggesting the BDH treatment rendered the CdTe surfaces equally clean in both cases. However, before BDH there were differences in the type of oxides detected by GIXRD and in the surface energy determined by the contact-wetting angle.

It has been shown that  $O_2$  is critical for the CdCl<sub>2</sub> treatment to achieve full impact on the device. This leads to concerns about sufficient circulation and replenishment of the  $O_2$  ambient during the CdCl<sub>2</sub> treatment in a static system. Humidity and exposure to high temperatures in presence of air can lead to oxide formation on the CdCl<sub>2</sub> source plate, leading to concern about their reuse. To study these variables, the spacing between the CdCl<sub>2</sub> plate and the substrate was varied during the CdCl<sub>2</sub> treatment. Increasing the distance would increase the availability of  $O_2$  at the CdTe surface. Cells made with fresh plates included those with 0 and 6X spacing where X is our standard spacing of ~0.6 mm. After being used for treating the cells with no spacing, the CdCl<sub>2</sub> plate was re-used for treating with 2X spacing. It was found that the largest spacing (6X) was best, demonstrating that the delivery of  $O_2$  and CdCl<sub>2</sub> plates had much lower efficiency and/or severe retrace instability. Following this result, fresh CdCl<sub>2</sub> plates were used for every treatment. The best device from this series was VT85.33-01, having  $V_{OC}$ =0.749 V,  $J_{SC}$ =22.9 mA/cm<sup>2</sup>, FF=65.2%, and eff.=11.2%.

# CdTe TFP Team Activity and Collaboration

IEC attended the National Team Meeting held at NREL on October 31 and November 1, 2002. We presented a grand summary of stress degradation effects on CdTe cells using data contained in Team Minutes of meetings from 1996 to present. We also presented on effects of post processing and anneal and CdCl<sub>2</sub> treatment on BP Solar films, on photoconductivity in CdS films and also on the effects of ambient on CdTe cells during stress treatments. We continued to support BP Solar through collaborative interactions.

We also attended the National Team meeting held at NREL on July 10 and 11, 2003. Two presentations were given, detailing humidity effects during post-deposition processing and stress. Brian McCandless visited First Solar September 23, 2003. IEC has sustained regular interaction with First Solar in the analysis and development of the back contact process. This has included characterization of surfaces by GIXRD, crosssection analysis by AFM, surface energy measurements, compositional analysis of alternative contact materials, and bias-stress studies.

## 2.3 Phase 3 Summary: 9/5/03 to 9/4/04

During this contract period substantial progress was made in understanding and controlling the CdTe surface chemistry, in determining the effect of humidity and precontact CdTe surface condition on stability, in developing transparent ZnTe:Cu contacts, in establishing reproducible CdTe deposition at high rate on a moving substrate in a vapor transport reactor, in making devices with 12-13% efficiency on commercial SnO<sub>2</sub>, and in developing new methods for device analysis.

Little is known regarding the effects atmospheric oxygen and humidity on device performance and chemistry during standard stress conditions. We have carried out a systematic investigation of the effects of stress in the dark and light at 80°C at various humidities on IEC and FS CdTe devices. The formation of TeO<sub>2</sub> is observed at 0% humidity but no  $TeO_2$  phases are observed at higher humidities.  $Cu_{2-x}Te$  in the back contact is observed at all humidities. The formation of a new phase, CuTeO<sub>3</sub>, is observed in the pattern for the 0% humidity stressed device. IEC cells exhibited forward-reverse retrace hysteresis prior to stressing which became worse with stressing. The 0% humidity stressed device showed the best stability despite the significant chemistry occurring in back contact during stressing. No back contact changes were detected by GIXRD for the FS stressed devices. All stressed FS devices exhibit J-V rollover at forward bias and decreased V<sub>OC</sub>, increasing in severity with higher stress humidity. The J-V data of the dark and illuminated humid stressed devices shows similar trends between the two stress conditions, though more rapid degradation is observed for the devices stressed under illumination. We have attributed the improved stability of the IEC devices to the thicker Te, which acts as a sink for excess Cu.

A common etchant used for CdTe device processing is the nitric acid/phosphoric acid mixture (NP), which produces a 50-100 nm crystalline Te layer on CdTe. Experiments were performed to study the autocatalytic nature of NP etching. When using fresh NP solutions it was observed that the etch rates of CdTe were considerably slower than expected. Subsequent etches in the same solution showed faster etching as evidenced by bubbling time, suggesting that a product of the reaction is itself involved in the reaction. Bubbling times were found to decrease with increasing NO<sub>2</sub><sup>-</sup>, with almost immediate bubbling observed with treatment of CdTe in NP containing 0.16M NaNO<sub>2</sub>. From these results, the use of NO<sub>2</sub><sup>-</sup> based etchants for CdTe back contacting appears promising and may benefit for CdTe device processing by allowing shorter immersion times, more efficient and controllable etching, and avoiding the use of concentrated HNO<sub>3</sub>.

The University of Toledo group has recently presented results regarding a new chemical treatment for CdTe device processing, where samples are illuminated while immersed in an aniline-based aqueous solution. IEC has collaborated with the University of Toledo to assist in understanding of the solution and surface chemistry that may be involved in the aniline-based process. VASE and GIXRD both confirm the presence of crystalline Te ~50-100 nm on the CdTe surface following successful treatments under illumination. Results were very sensitive to the illumination during the treatment. A successful treatment requires the presence of aniline, Cl<sup>-</sup> ions, O<sub>2</sub>, consistent illumination and careful control of pH. Devices have been processed using aniline treatments under illumination and careful control of pH. Devices have been processed using aniline treatments under illumination and completed with Cu-containing back contacts and graphite paste. Initial devices show very promising performance, with V<sub>OC</sub> of ~800 mV, J<sub>SC</sub> ~20 mA cm<sup>-2</sup>, and fill factor ~60% or higher. We conclude that a successful aniline treatment of CdTe results in the formation of a crystalline Te-rich surface layer on the CdTe surface, which will be beneficial for back contact processing.

Development of ZnTe:Cu contacts has been motivated by the high p-type conductivity of the ZnTe, needed for low contact resistance, and as a source of Cu doping the CdTe, needed for high  $V_{OC}$ . In addition, ZnTe can serve as a semi-transparent back contact for bifacial JV and QE measurements, to provide new insight on the device physics and back junction properties, and as a transparent contact for the top cell of a polycrystalline tandem. During the present contract period, IEC investigated the galvanic solution growth of ZnTe. Tri-ethylamine (TEA) was investigated as a complexing agent to control the chemical reactivity of the Cu in the solution. Cells with optimum TEA had 10% efficiency and negligible hysteresis. The light JV curve indicates a weakly blocking contact when illuminated from front (through glass) but when illuminated from back (through ZnTe) does not have a blocking contact. This indicates that the back contact is photoconductive. Backwall QE measurements through the transparent ZnTe:Cu/ITO shows the response is largely limited to carriers generated very near the CdS junction. There is no evidence of collection at a back junction, nor is there evidence of much collection throughout the CdTe which implies a low lifetime and low field in the bulk of the CdTe.

Increasing  $V_{OC}$  with the thin CdS needed for maintaining high Jsc requires reducing the effect of pinholes or regions of non-uniform CdS. The degree of spatial non-uniformity can be directly measured using a modified scanning probe microscope (SPM). We have refined sample preparation procedures to yield polished cross-sections of working cells and have modified SPM for operation in different electrical configurations. Electric field gradient (EFG) measurements have been made with and without additional illumination and at different junction bias. Measurements made at forward and reverse bias and at different illumination conditions revealed marked changes in gradient and have yet to be fully interpreted.

Several baseline VT devices were fabricated to compare with 60 nm thick  $Ga_2O_3$  and  $In_2O_3$  high resistance transparent (HR) layers. CdS films were deposited by chemical surface deposition to a thickness of 100 nm. Cells with a  $Ga_2O_3$  HR layer had  $V_{oc}$  of ~0.79 V and efficiency of ~12% while those with an  $In_2O_3$  HR layer had  $V_{OC}$  ~0.60 V

and efficiency of 8%. Therefore,  $Ga_2O_3$  HR layers were used in subsequent VT device studies.

Significant design modifications were made to the vapor transport source to increase CdTe utilization and to improve repeatability and overall robustness. The pre-deposition and post-deposition zone heaters were replaced. The new heaters use Tantalum wire looped between a sheet of Vycor glass and a grooved boron nitride plate. A new source was designed and fabricated. The most significant change was the method of delivering heat to the ampoule. Problems with the original design resulted in contamination of the CdTe from the filament as well as significant CdTe deposition onto the inside surfaces of the manifold. The CdTe utilization at the substrate with this source had been 10-20%. The contamination resulting from filament degradation, especially Si and Al, caused shunting and poor efficiency and was verified by SIMS. The new design utilizes a double-wall cylindrical boron nitride source heater to heat the quartz ampoule containing the CdTe charge. Over the range of experimental conditions, re-sublimation of the deposited film is not a critical issue and the CdTe utilization is found to be  $50\% \pm 5\%$ . All films exhibit faceted morphology, with means lateral grain size proportional to film thickness. Grains with lateral dimension comparable to film thickness, ~ 6 µm, are found at 550 and 570°C substrate temperature, but the average grain size is higher and the distribution of sizes is narrower at 570°C.

Alternative processes for treatment in  $Cl_2$  or HCl vapor have also been examined. Two atmospheric pressure approaches for delivery of  $CdCl_2$  vapor species were considered: diffusion in parallel-plate configuration and vapor transport via carrier gas in a packed bed. In both approaches, the diffusion of  $CdCl_2$  through ambient gas is a critical aspect for estimating concentration at the film surface. Although comparable standard deviations were found for the wet and parallel plate vapor treatments, the highest performance, with efficiency = 12%,  $V_{OC} > 800$  mV and FF > 73%, was obtained with parallel-plate  $CdCl_2$ vapor treatment. The cells made with packed bed  $CdCl_2$  treatment had lower performance and uniformity.

The sensitivity of cell performance to VT deposition and post-deposition processing, in particular the effect of CdTe growth rate and CdCl<sub>2</sub> vapor treatment, was evaluated using CdTe from the newly modified VT reactor. All samples were fabricated on TEC15 soda-lime glass/SnO<sub>2</sub>, with 60 nm Ga<sub>2</sub>O<sub>3</sub> HR layer and 80-90 nm CdS. The CdTe films were deposited at 20 Torr using He carrier gas and an O<sub>2</sub> base pressure of ~ 0.02 Torr. There are four key conclusions. First, equivalent results were obtained with and without a post-deposition anneal at T>550°C in argon, showing that the anneal step is unnecessary, unlike PVD and electrodeposited cells, in which best results are obtained with an annealing step prior to CdCl<sub>2</sub> treatment. Second, cells with no CdCl<sub>2</sub> treatment exhibit marked photo-response, indicating that the high deposition temperature yields an active junction, again in contrast to PVD or electrodeposition. Third, similar results were obtained over the range of static equivalent growth rate, from 7 to 12 µm/min and deposition temperature, from 550°C to 570°C. Fourth, nominally similar performance was obtained for vapor CdCl<sub>2</sub> treatment from 405°C to 425°C for 20-25 min but the highest V<sub>OC</sub>'s were obtained over a narrower range, from 405°C to 410°C. Cells with no

post-deposition Cl treatment exhibited the lowest blue response (thickest CdS) and the lowest absorber band edge (highest band gap), consistent with no CdS diffusion into the CdTe. The other samples show a similar range of blue response and similar long wavelength fall-off, consistent with CdS loss  $\approx 10$  nm and formation of CdTe<sub>1-x</sub>S<sub>x</sub> with x < 0.05, respectively. QE measurements at reverse bias confirm that losses in J<sub>SC</sub> are due to absorption not collection losses. Devices with V<sub>OC</sub>>0.80 V and FF>68% were obtained on pieces from multiple runs using Au/Cu evaporated contacts. The highest efficiency was on piece VT118.4 with Voc=0.808V, Jsc=23.8 mA/cm2, FF=69.2%, and efficiency=13.3%.

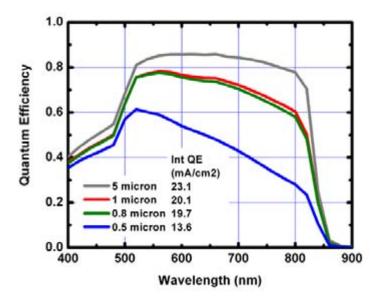

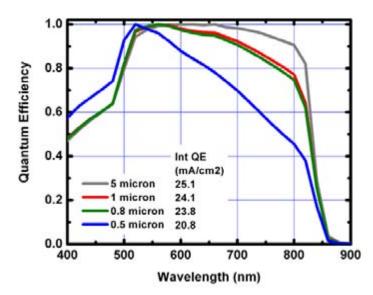

Voltage dependent photocurrent collection losses can be especially significant in CdTe solar cells, primarily reducing the fill factor. We analyzed the  $J_L(V)$  effect in CdTe solar cells by measuring current-voltage curves J(V) at different intensities and using the difference to quantify  $J_L(V)$  similar to previous work at IEC on CIGS. We have analyzed over 10 CdTe devices from 4 different CdTe sources having FF from 50 to 72 and thicknesses from 1.8 to 5 µm. All show significant  $J_L(V)$  losses affecting the maximum output power and FF. Recalculating the FF without these losses results in a 5-15% point increase. Voltage dependent collection in CdTe solar cells increases after stressing. This effect is well described using the uniform field model as was developed for *p-i-n* solar cells. Numerical simulations with AMPS support the experimental results.

Measurements of  $V_{OC}$  (T) shows linear fit from 220 to 320K on most CdTe devices over a range of intensity with an extrapolated intercept of ~1.5 eV consistent with the CdTe bandgap. However, we have found that at lower temperatures, the  $V_{OC}$  becomes independent of light intensity and temperature, saturating at about  $V_{OC}$ =1.0 V. We suggest that this upper limit represents a fundamental parameter, the built-in voltage. Saturation of  $V_{OC}$  indicates carrier freeze-out. When there are no longer sufficient free carriers, the quasi-Fermi levels no longer respond to changes in carrier generation or temperature.  $V_{OC}$  reaches its maximum value determined by the absorber bandgap and the contact potentials. The saturated value of  $V_{OC}$  decreases after stress from ~1.0V to ~0.90-0.95 V.

#### CdTe TFP Team Activity and Collaboration

The Institute has maintained a high level of collaboration with CdTe Thin Film Partnership team members. Towards the goal of helping First Solar to develop vapor CdCl<sub>2</sub> treatments, IEC: constructed a new CdCl<sub>2</sub> source generator at IEC to carry out experiments compatible with First Solar; carried out experiments to directly compare treatment in CdCl<sub>2</sub> vapor with treatment of CdCl<sub>2</sub>-coated samples; submitted detailed reports on modeling CdCl<sub>2</sub> vapor delivery; and investigated source-poisoning issues associated with oxide formation in the source generator. IEC performed GIXRD measurements on a large number of CdTe films at different stages of processing and for different back contact processing conditions. IEC characterized the structure and composition of the back contact surface of First Solar production plates and of newly developed contacts made by a third party company for First Solar. IEC has also been assisting in the analysis of CdS film properties, CdTe-CdS interaction after processing, and CdS/TCO quality assurance issues for First Solar. IEC received a set of samples from First Solar including baseline devices, as well as those having unusual J-V performance. Complete analysis of J-V-T and QE(V) was performed and reported at the team meeting along with results on similar samples by CSU and USF.

Collaboration with Canrom has also been on-going, with respect to post-deposition processing methods for Canrom CdTe/CdS and to the Team-related issue of evaluation of humidity during cell stress. This follow-up to the samples stressed in the dark at 85°C at different humidities consist of repeating the stress conditions but in the light with the calls at  $V_{OC}$ . Results were presented at the team meeting and in this report.

We also provided devices to CSM for cross-sectional luminescence measurements.

Four members of IEC (Darshini Desai, Kevin Dobson, Brian McCandless and Steve Hegedus) attended the CdTe National Team Meeting in Toledo, February 2004. Much of the work presented there is also contained in this report. Topics included the chemistry of the aniline bath treatment of CdTe, the effects of humidity stress of CdTe under illumination; temperature dependence of Voc to characterize recombination; voltage dependence of photocurrent to evaluate FF losses; and work related to the FS vapor-CdCl<sub>2</sub> treatment.

# 2.4 Phase 4 Summary: 9/5/04 to 9/4/05

Research on CdTe-based solar cells includes five tasks: (1) High Throughput CdTe Processing; (2) Back Contact Processing Options; (3) ZnTe:Cu Semi-Transparent Contacts for Bifacial Device Analysis; (4)Understanding and Improving V<sub>oc</sub>; and (5) Accelerated Stressing.

Processing options, which address a number of critical issues relating to processing of thin-film CdTe/CdS devices have been addressed. The window layer properties, including configuration, composition and thickness have been shown to have a significant effect on final device performance. We have selected Ga<sub>2</sub>O<sub>3</sub> as the best high resistance interface layer for our process. Engineering and thermo-chemical aspects of the postdeposition CdCl<sub>2</sub> treatment of CdTe were investigated. Annealing CdTe films in the presence of CdCl<sub>2</sub> and O<sub>2</sub> promotes CdS diffusion into CdTe and also shifts the chemical equilibrium of the film surface, which may influence the bulk electrical properties of the CdTe. Comparisons of wet and vapor CdCl<sub>2</sub> treatment were discussed including the development of a packed bed reactor for vapor CdCl<sub>2</sub> treatments. High efficiency with good spatial uniformity was achieved with vapor CdCl<sub>2</sub> treatment. Careful control of the O<sub>2</sub> and humidity in the anneal atmosphere is required to avoid the formation of deleterious oxides, which will affect the Cd-vacancy concentration within the CdTe film, leading to poor device performance. High throughput was evaluated by increasing the CdTe deposition rate to 9 µm/min, reducing the CdCl<sub>2</sub> treatment time while increasing the treatment temperature, and reducing the CdTe thickness. VT devices with 5-7 µm

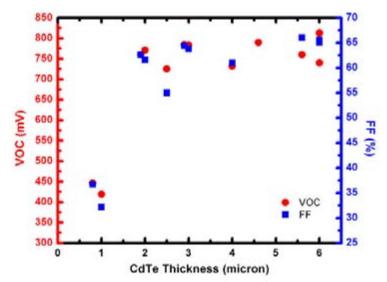

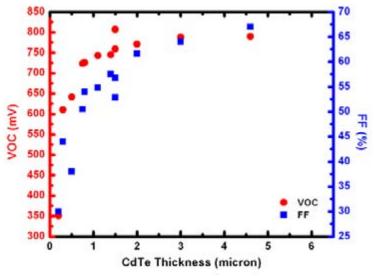

thick CdTe deposited on moving substrates at 9  $\mu$ m/min using a 20 min vapor CdCl<sub>2</sub> treatment at 415°C achieved V<sub>oc</sub> up to 840 mV and efficiency > 13%. Devices with efficiency of 11% were obtained with 2 min CdCl<sub>2</sub> treatments at 465°C. For cells with CdTe thickness ~1.5  $\mu$ m, efficiency >10% was obtained . V<sub>oc</sub> and FF decreased for cells with CdTe deposited at >80  $\mu$ m/min and for cells with CdTe thinner than 1.5  $\mu$ m.

A number of steps are required for successful processing of back contacts to CdTe; removal of any oxides, the formation of a Te-rich surface, application of a Cu source, contact annealing and deposition of a secondary contact. A number of methods can be used for each of these steps. Consideration of different processes should include simplicity and ease of industrial scale up. The nature of each process may also be critical for contact and device stability. A thorough knowledge of etching mechanics will allow the development of alternate or modified etches that may be more efficient and faster, perhaps through the use of catalysts, and safer to use, all of which will assist possible industrial scale-up of CdTe technology. The results obtained from monitoring the etching processes have also highlighted the usefulness of VASE and GIXRD as diagnostic tools for monitoring the quality of material surfaces during processing.

The Te rich surface can be formed by wet chemical etching or by 'dry' deposition of Te, however, application of Cu should be carried out immediately, to prevent atmospheric oxidation of the Te-rich surface. A number of simple methods of Cu application have been studied including Cu metal, CuCl doped graphite, dipping in CuCl, and Cu-doped ZnTe. Contact annealing should be carried out in an inert atmosphere to avoid oxidizing the back contact. A full understanding of the role of Cu and other possible contact metals in the back contact chemistry and their behavior within the CdTe/CdS structure is required before optimization of device performance and stability can be obtained.

The use of an aniline-based treatment for back contact processing of CdTe/CdS devices was investigated. The treatment was found to form reproducible Te-rich CdTe surfaces, similar to oxidizing etches, which would be expected to allow processing of improved Cu-based back contacts. Analysis of bath conditions highlights that the presence of aniline, Cl<sup>-</sup> ions, dissolved O<sub>2</sub>, consistent illumination and control of pH are critical for successful treatments. A photocatalytic mechanism is proposed, involving the reduction of dissolved  $O_2$  by conduction band electrons to produce  $H_2O_2$  or similar, which etches the CdTe. The reduction is complemented by the oxidation of aniline by valance band holes. Best device results, with efficiencies  $\sim 12\%$ , have been obtained for treatment times as short as 30 min. At longer treatment times, device performance decreases, though the effect is not as severe as has been observed with over-treatment of CdTe in oxidizing etches. Criteria for possible substitutes for the toxic aniline are presented. Results of potential substitutes are discussed. A crucial advantage of aniline is that it is compatible with thinner CdTe films. Unlike more aggressive etches like BDH or NP, aniline etching gives a high yield and negligible shunting with CdTe devices  $< 3 \,\mu m$ thick.

Cu-doped ZnTe films grown by galvanic deposition were developed to provide transparent ohmic contacts to CdTe solar cells. Control of the Cu doping with

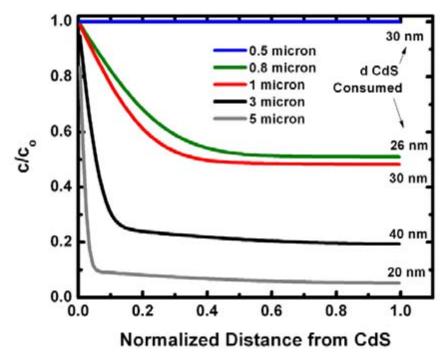

triethanolamine was critical to limit the free Cu in order to achieve high transparency (>60% in the visible) and to minimize shunting. Devices with ZnTe:Cu contacts had comparable performance to devices with Cu/Au or Cu/Ni contacts, achieving V<sub>OC</sub> of 0.82 V and fill factor (FF) of 68% for standard front illumination. The ability to form a low barrier, Ohmic contact with ZnTe:Cu depends on the CdTe surface treatment and results in formation of a thin Cu<sub>2</sub>Te interlayer, verified by GIXRD. Typically, devices with BDH or anilene treatments had better forward bias behavior and do not exhibit roll-over beyond V<sub>OC</sub>, indicating an ohmic low barrier contact has been formed. Devices with Brmethanol had lower FF and exhibited rollover. Bifacial spectral response (SR) measurements, through front and back contacts, were analyzed and yielded a diffusion length (L) of 0.8  $\mu$ m and depletion width (W) of 2.5  $\mu$ m for 5  $\mu$ m thick CdTe cells. Backwall SR measurements made through the transparent ZnTe contact are much more sensitive to L and W than are measurements for standard front illumination. ZnTe:Cu is a promising material for bifacial characterization as well as tandem cell interconnects and more stable Cu-doped contacts. Characterization of devices with CdTe layer thickness from 1.5 to 10 µm is in progress. Accelerated stress testing on devices with ZnTe:Cu contacts with different concentrations of Cu is planned.

Changing the bias voltage, light intensity and temperature during stress can induce transient degradation or recovery in  $V_{OC}$  of CdTe solar cells. Simulated day/night cycles leads to daily degradation in the light and recovery in the dark. Greater recovery in the dark and less bias dependence is correlated with better overall stability. These transients complicate the correlation between cell (indoor) and module (outdoor) performance. Results are consistent with changes in electronic states and recombination. No single stress protocol is likely to identify all instability mechanisms.

Increasing V<sub>oc</sub> in VT CdTe/CdS cells to >900 mV and maintaining it in cells with submicron thick CdTe layers requires an understanding of existing cells, determination of the recombination sources in the cell, quantifying the influence of back contact on V<sub>oc</sub>, especially in thin devices, and assessing changes induced by depositing onto a moving substrate at elevated rate (>10  $\mu$ m/min). The problem has two parts: 1) defining limits to V<sub>oc</sub> in CdTe solar cells in general and 2) defining the influence of VT processing, especially in thinner cells.

We have found that the following empirical factors affect  $V_{oc}$  in present-generation VT CdTe devices. When initial  $d_{CdS} < 80$  nm or final  $d_{CdS} < 40$  nm, a buffer layer is needed to maintain  $V_{oc}$ . The highest  $V_{oc}$  is obtained for CdTe deposition >500°C.  $V_{oc}$  decreases as CdTe thickness decreases to  $d_{CdTe} < 1.5 \mu m$ . Thinner CdTe requires re-optimization of the CdCl<sub>2</sub> temperature time cycle and a less penetrating surface etch, such as anilene instead of BDH. The CdCl<sub>2</sub> surface is critical to device performance with aging reducing the effectiveness of the CdCl<sub>2</sub> treatment, including reduction in  $V_{oc}$  and yield. High  $V_{oc}$  requires an O<sub>2</sub> partial pressure during VT growth. Cu in the contact does not appear to be necessary for  $V_{oc} \sim 0.78V$  but Cu + HT is necessary for  $V_{oc}$ >0.80V. We have determined that a back contact barrier has no effect on  $V_{oc}$ , at least for devices with 3-4 µm CdTe, consistent with recontacting studies from several years ago. Eliminating voltage dependent collection has little effect on improving  $V_{oc}$  on devices with FF>65% but can

have significant improvement on cells with FF<60%. The upper limit to  $V_{oc}$  obtained at low temperature is around 1 V, suggesting this is the built-in potential. The highest  $V_{oc}$  at 28°C obtained this year was 0.84V.

## CdTe TFP Team Activity and Collaboration

Support of the National CdTe R&D team continued through sub-team leadership, bifacial and stress analyses, and film/cell supply to other team members. Unprocessed and CdCl<sub>2</sub> treated PVD and VT CdTe/CdS stacks were sent to Colorado State University for photoluminescence investigations of defects. Completed devices were sent to Colorado School of Mines for investigation of defect levels by admittance spectroscopy. The cell fabrication matrix evaluated was: with/without CdCl<sub>2</sub> treatment, with/without Cu, and with less and more intrusive etching prior to metallization. Preliminary results of these studies were presented at the Team meeting held in May 5-6, 2005. IEC made presentations at the team meeting: "Bifacial CdS/CdTe/ZnTe Device Characterization", "Effect of Applied Bias during Stress", and "Sensitivity of CdTe/CdS Device Operation to Processing Variations". IEC provided extensive analysis of Cu<sub>x</sub>Te back contacts developed by Ceramem Corporation using nanoparticle precursors. On-going collaboration with the University of Toledo continued on the fundamental surface chemistry associated with aniline treatments. IEC also conducted bias-dependent tensile pull tests of as-deposited and stressed UT cells to elucidate changes induced by processing and stress variations. In these cells, the adhesion of all layers was sufficiently high that failure occurred either at the epoxy-cell interface or via glass cracking, which is a tacit demonstration that cells with metallized contacts can exhibit high mechanical durability. Other activities included providing VT samples to McMaster Energy Enterprises (aka Solar Fields) for start-up development of post deposition processing, providing NREL with technical details of the IEC VT system, and teaching the chemical surface deposition (CSD) technique to several groups.

## 2.5 Phase 5 Summary: 9/5/05 to 3/31/07

The CdTe cell fabrication effort focused on CdTe deposition and post deposition processing to increase throughput by decreasing processing step time and reducing CdTe film thickness. Effort was also directed at handling and processing issues which affect baseline cell efficiency. The effect of carrier gas composition and substrate temperature on vapor transport (VT) CdTe film growth and device performance was evaluated. Vapor CdCl<sub>2</sub> treatments, which allow the treatment temperature to be separated from the CdCl<sub>2</sub> and O<sub>2</sub> concentration, were refined to allow a new baseline process to be defined with treatments ~ 2 minute in duration. Reduction in treatment time required increasing the treatment temperature of the CdTe/CdS and maintaining the partial pressures of CdCl<sub>2</sub> and O<sub>2</sub> to ~5 mTorr and 120 Torr, respectively. Similarly, the aniline photoactivated surface treatment was refined to permit effective Te formation in less than 5 minutes, by increasing the intensity of the incident light. In the area of device performance, analysis of J(V) curves has indicated that most CdTe cells can be described with three circuit elements: by a single forward diode (given by A, J<sub>0</sub>), a resistance (R), and a voltage dependent photocurrent  $(J_{L0} * \eta(V))$ . Systematically determining these parameters and evaluating their impact on efficiency shows that our typical VT device with 13% efficiency could be 16% efficient in the absence of R and voltage dependent collection. This sets an upper limit based on the junction recombination.

Different aspects of processing VT solar cells were evaluated, and new processing options to address key issues of high throughput are being developed. In particular, variations in device performance are correlated with systematic variations in the CdCl<sub>2</sub> treatment and with the exposure of fresh CdTe surfaces to humid ambient prior to CdCl<sub>2</sub> treatment. With respect to CdTe deposition, characterization of the VT deposition system was carried out to refine the quantitative model used to monitor the deposition rate and Cd utilization. With respect to surface treatments for back contact processing; alternatives to BDH processing, such as aniline treatment, continue to be investigated. Temperature dependant bifacial QE measurements gave new insights into the CdTe device physics. The formation rate and composition of oxide phases in CdTe films was further quantified with respect to humidity.

Voltage dependence of the photocurrent  $J_L(V)$  of CdTe/CdS solar cells has been characterized by separating the forward current from the photocurrent at several intensities. The primary mechanism of photocurrent collection in CdTe solar cells illuminated through the front CdS is field-assisted drift in the depletion region.  $J_L(V)$ reduces the fill factor (FF) of typical cells by 10-15 points, the open circuit voltage (V<sub>OC</sub>) by 20-50 mV, and the efficiency by 2-4 points. A single carrier Hecht model developed for drift collection in *p-i-n* solar cells gives a good fit to the data for CdTe thickness from 1.8 to 7.0 µm and yields a fitting parameter consistent with lifetimes of 10<sup>-9</sup> sec, as measured by others. Accelerated thermal and bias stressing increases  $J_L(V)$  losses.

Bifacial analysis provides quantitative insight into CdTe device operation by separating the effects of front and back junction. Semi-transparent ZnTe:Cu contacts were developed and applied to CdTe devices with varying thickness (t) to determine the diffusion length (L), and depletion width (W) from analysis of the back spectral response (SR<sub>B</sub>). Front spectral response (SR<sub>F</sub>) is nearly unaffected by L. SR<sub>B</sub> and back J<sub>SC</sub> are higher for thinner cells as SR<sub>B</sub> is limited by diffusion across the field free region that is smaller for thinner cells. Bifacial characterization results indicate a photosensitive back barrier. There is no evidence of a back junction in these cells. A single junction determines recombination current.

#### CdTe TFP Team Activities and Collaborations

Collaborations under the Thin Film Partnership were conducted with groups at the University of Toledo (UT), Colorado School of Mines (CSM) and at the National Renewable Energy Laboratory (NREL). CdS films on Ga<sub>2</sub>O<sub>3</sub>-coated TEC15 and Ga<sub>2</sub>O<sub>3</sub>/ITO-coated flexible Pilkington glass substrates were sent to UT for stress-piezoelectric analysis and device fabrication. Completed VT cells fabricated with and without CdCl<sub>2</sub> treatment and Cu contacts were supplied to CSM for admittance

spectroscopy analysis in an effort to correlate these processing variables with the spectral signatures indicative of defect levels. Several sets of VT devices were fabrication using TCO and TCO/HR and TCO/CdS provided by the CdTe group at NREL. IEC attended the National CdTe R&D Team meeting on March 9-10, 2006. Brian McCandless co-led the Materials Chemistry sub-team with Tim Ohno (CSM) and made presentations in sessions for the Device Physics and Materials Chemistry teams and at a workshop focused on CdTe solar cell open circuit voltage.

## 2.6 Phase 6 Summary: 4/1/07 to 12/31/07